# ACTIVE MESSAGES AS A SPANNING MODEL FOR PARALLEL GRAPH COMPUTATION

## Nicholas Edmonds

Submitted to the faculty of the University Graduate School in partial fulfillment of the requirements for the degree

Doctor of Philosophy in the School of Informatics and Computing Indiana University

December 2013

| Accepted by the Graduate Faculty, Indiana Uments for the degree of Doctor of Philosophy | Jniversity, in partial fulfillment of the require-<br>y. |

|-----------------------------------------------------------------------------------------|----------------------------------------------------------|

|                                                                                         |                                                          |

|                                                                                         |                                                          |

|                                                                                         | Andrew Lumsdaine, Ph.D.                                  |

|                                                                                         | Arun Chauhan, Ph.D.                                      |

|                                                                                         | Alex Pothen, Ph.D.                                       |

|                                                                                         | Dirk Van Gucht, Ph.D.                                    |

|                                                                                         | Thomas Sterling, Ph.D.                                   |

|                                                                                         |                                                          |

Copyright 2013 Nicholas Edmonds All rights reserved

| This thesis is dedicated to Linda and Lonne Edmonds, who dedicated countless hours to inspiring my love of learning and respect for knowledge. |

|------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                |

|                                                                                                                                                |

|                                                                                                                                                |

|                                                                                                                                                |

| iv                                                                                                                                             |

# Acknowledgements

This thesis has been a long process that would not have been possible without the help and support of a number of incredible friends and colleagues.

Firstly I thank my committee: Andrew Lumsdaine, Arun Chauhan, Alex Pothen, Dirk Van Gucht, and Thomas Sterling. Their time and attention and the valuable perspectives they contributed enabled this work to be greater than I could have made it on my own.

Particular thanks are due to Andrew Lumsdaine for his patience and for providing an environment in which to explore my intellectual curiosities. He taught me the difference between science and engineering and encouraged me to be the most intellectually honest scientist that I could be. His ability to provide much needed guidance when I had lost my path and to help me distill the core insights from my research were invaluable.

While I may be receiving my degree from the School of Informatics and Computing due to organizational changes, the formative years of my graduate education took place under the impeccable tutelage of the faculty of the Computer Science Department in the College of Arts and Sciences at Indiana University. They deserve no small amount of credit for this work.

As a newly accepted 20-year old Ph.D. student I wasn't quite sure what I had signed up for, but I knew that I wasn't ready to be done with my formal education. Jeremy Siek and Katie Siek (then Moor) taught me how grad school worked, introduced me to key future colleagues, and proved to be great friends.

The Open Systems Lab was an excellent environment in which to develop my ideas as well as a rich source of opportunities for collaboration. I am indebted to all the OSL members I shared room 415, and later 135, with in Lindley Hall.

In particular, Doug Gregor introduced me to generic programming in C++ and developed the initial version of the Parallel Boost Graph Library which would form the basis for my eventual thesis as well as a number of publications along the way. Without his influence it's a safe bet that this thesis would not exist.

Brian Barrett was tireless when it came to answering my questions about HPC architecture and MPI implementation details.

Joseph Cottam was invaluable in editing and reviewing drafts of my publications that were no doubt much improved by his comments. He also helped generate high-quality visualizations used in many of my publications that were better than anything I could have done alone.

Ben Martin was always willing to pitch in on projects and improved every one in which he participated.

Jeremiah Willcock and Torsten Hoefler were instrumental in making the application stack presented here a reality. The three of us laid a solid foundation in AM++ and Active Pebbles upon which this work is based.

Chris Mueller was instrumental in my joining the OSL and, in addition to fruitful academic collaboration, inspired me to seek adventure. Without his influence I may never have discovered the mountains and foreign lands that so often served as a refuge during my graduate career.

I would be lost without the support of the amazing staff that that made everything run smoothly so that I could focus on research. Lucy Battersby, Rob Henderson, and the rest of the Indiana University Computer Science Department provided an outstanding work environment. I felt Lucy's absence at the end of my graduate career and no doubt many future graduate students will be worse off for not having known her.

Rebecca Schmitt and Kelsey Allen in the Center for Research in Extreme Scale Technologies went above and beyond to help me out of more than a few binds. Their excellent organizational skills played a large part in the success of many grants that supported my research.

Finally, Erin Dobias was resolute in her support and refused to let me settle for anything but success. Nietzsche said that, "Many are stubborn in pursuit of the path they have chosen, few in pursuit of the goal." She helped me to remember to focus on the goal.

#### Nicholas Edmonds

# ACTIVE MESSAGES AS A SPANNING MODEL FOR PARALLEL GRAPH COMPUTATION

Graph applications are members of an increasingly important class of applications that lack the natural, or domain-induced, locality of traditional computational science problems induced by large systems of PDEs. Rather than being analytically deducible, the dependency structure of graph applications is determined by the input graph itself. This data-carried dependency structure is expressed at run time and offers limited opportunities for static analysis. Graph applications present challenges with regard to load balancing, resource utilization, and concurrency at HPC scales.

This thesis presents a set of parallel programming abstractions and a software-design methodology that allows for the implementation of flexible, scalable, and highly concurrent graph algorithms. The use of active messages as the underlying communication mechanism provides three key performance benefits over more coarse-grained approaches. First, this phrasing reduces global synchronization and exposes asynchrony that can be used to hide communication latency. Second, by executing and retiring messages as they are received, memory utilization is reduced. Finally, each active message represents an independent quantum of work that can be executed in parallel. By ensuring atomicity of the underlying vertex and edge properties manipulated by messages, fine-grained parallelism can be employed at the message level. The implementation of these ideas is presented in the context of the Parallel Boost Graph Library 2.0.

This library is distinguished from other parallel graph implementations by two key features. By moving computation to data, rather than vice-versa, the effects of communication latency are reduced. Simultaneously, runtime optimization separates algorithm specifications from the underlying implementation. This allows optimization to be performed as the structure of the input graph, and thus the computation, is discovered. Separating specification from implementation also provides performance portability and enables retroactive optimization.

The generic design of the library provides a common framework in which to experiment with dynamic graphs, dynamic runtimes, new algorithms, and new hardware resources. Most importantly, this thesis demonstrates that phrasing graph algorithms as collections of asynchronous, concurrent, message-driven fragments of code allows for natural expression of algorithms, flexible implementations leveraging various forms of parallelism, and performance portability—all without modifying the algorithm expressions themselves.

| Andrew Lumsdaine, Ph.D. |

|-------------------------|

| <br>Alex Pothen, Ph.D.  |

| Arun Chauhan, Ph.D.     |

| Dirk Van Gucht, Ph.D.   |

| Thomas Sterling, Ph.D.  |

# Contents

| List of | Figures                                                              | xiii |

|---------|----------------------------------------------------------------------|------|

| List of | Acronyms                                                             | xvi  |

| Chapte  | er 1. Introduction                                                   | 1    |

| 1.1.    | Programming Models and Graph Computation                             | 3    |

| 1.2.    | Runtime Optimization                                                 | 5    |

| 1.3.    | Separating Expression from Execution                                 | 7    |

| 1.4.    | Elements of an Active Message Graph Library                          | 8    |

| 1.5.    | Evaluation and Contribution                                          | 11   |

| 1.6.    | Conclusion                                                           | 12   |

| Chapte  | er 2. HPC Programming Models, Runtimes, and Parallel Graph Algorithm |      |

|         | Implementations                                                      | 13   |

| 2.1.    | Runtime Support for HPC Applications                                 | 14   |

| 2.2.    | Architectures, Languages, and Programming Models                     | 15   |

| 2.3.    | Parallel Graph Algorithm Implementations                             | 17   |

| 2.4.    | Active Messages                                                      | 21   |

| 2.5.    | Distributed Shared Memory and Transactional Memory                   | 23   |

| 2.6.    | Conclusion                                                           | 24   |

| Chapto  | or 3 Conoralized Active Messages                                     | 27   |

| 3.1.   | Design Philosophy                                       | 29  |

|--------|---------------------------------------------------------|-----|

| 3.2.   | Message Transport                                       | 31  |

| 3.3.   | Message Set Optimization                                | 33  |

| 3.4.   | Epoch Model and Termination Detection                   | 35  |

| 3.5.   | Progress and Message Management                         | 37  |

| 3.6.   | Benchmarks                                              | 38  |

| 3.7.   | Conclusion                                              | 48  |

| Chapte | er 4. Separating Specification from Implementation      | 50  |

| 4.1.   | Active Pebbles Programming Model                        | 52  |

| 4.2.   | Active Pebbles Execution Model                          | 59  |

| 4.3.   | Application Examples                                    | 67  |

| 4.4.   | Retroactive Optimization                                | 75  |

| 4.5.   | Conclusion                                              | 77  |

| Chapte | er 5. Classification of Parallel Graph Algorithms       | 79  |

| 5.1.   | Elements of Graph Algorithm Performance                 | 81  |

| 5.2.   | Wavefront Expansion (Label-Setting)                     | 83  |

| 5.3.   | Wavefront Expansion (Label-Correcting)                  | 86  |

| 5.4.   | Parallel Search                                         | 89  |

| 5.5.   | Coarsening and Refinement                               | 90  |

| 5.6.   | Iterative Methods                                       | 93  |

| 5.7.   | Combinations of These Patterns                          | 94  |

| 5.8.   | Conclusion                                              | 95  |

| Chapte | er 6. Expressing Graph Algorithms Using Active Messages | 96  |

| 6.1.   | Generic Graph Library Design                            | 100 |

| 6.2.   | Converting Algorithms to Active Messages                | 111 |

| 6.3.   | Graph Application Stack                                 | 114 |

| 6.4    | Supporting End-User Behavioral Modification             | 116 |

| 6.5.    | Conclusion                                                             | 119 |

|---------|------------------------------------------------------------------------|-----|

| Chapte  | er 7. Exposing Asynchrony and Parallelism                              | 121 |

| 7.1.    | Controlling Granularity and Avoiding Global Synchronization            | 124 |

| 7.2.    | Performance Comparison to BSP Graph Algorithms                         | 127 |

| 7.3.    | Implementation Details                                                 | 128 |

| 7.4.    | Conclusion                                                             | 136 |

| Chapte  | er 8. Incorporating Traditional PGAS Semantics                         | 138 |

| 8.1.    | The Case for PGAS Extensions                                           | 139 |

| 8.2.    | Generic Programming and the Distributed Property Map                   | 141 |

| 8.3.    | Distributed Property Map Semantics                                     | 143 |

| 8.4.    | Implementation                                                         | 147 |

| 8.5.    | Extensions                                                             | 149 |

| 8.6.    | Conclusion                                                             | 151 |

| Chapte  | er 9. Future Directions                                                | 153 |

| 9.1.    | Dynamic Runtimes                                                       | 154 |

| 9.2.    | Dynamic Graphs                                                         | 157 |

| 9.3.    | Runtime-Managed Shared-Memory Parallelism                              | 161 |

| 9.4.    | Motivating Application: Low-latency Query Processing in Dynamic Graphs | 162 |

| Chapte  | er 10. Conclusion                                                      | 164 |

| Bibliog | graphy                                                                 | 167 |

# List of Figures

| 2.1 | Comparison of AM++ vs. other active message implementations                  | 22 |

|-----|------------------------------------------------------------------------------|----|

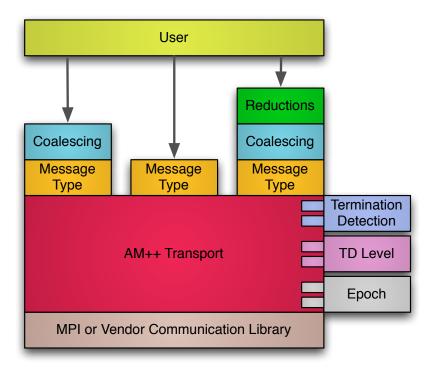

| 3.1 | Design of AM++.                                                              | 30 |

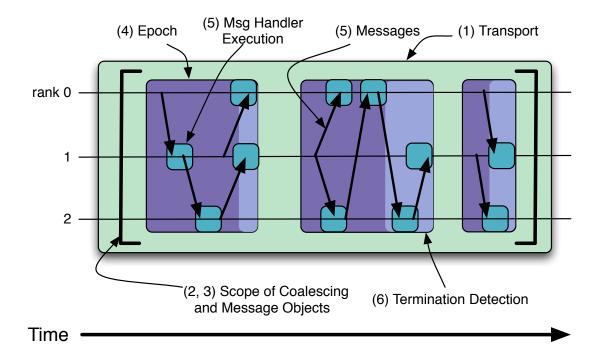

| 3.2 | The overall timeline of a program using AM++. Parenthesized numbers refer to |    |

|     | the preceding list of steps.                                                 | 31 |

| 3.3 | Example usage of AM++.                                                       | 33 |

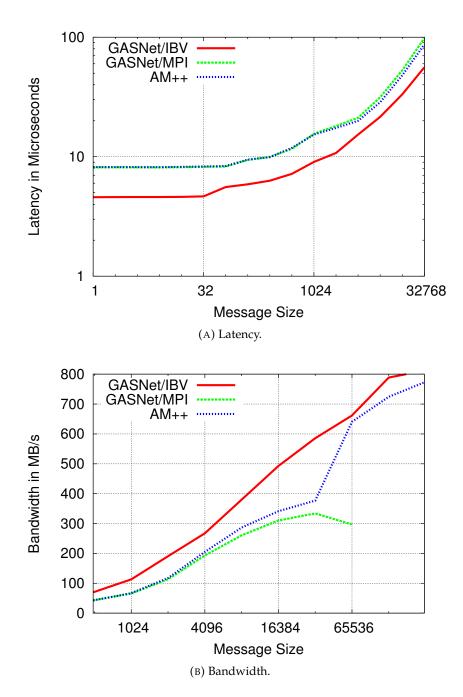

| 3.4 | GASNet over MPI or InfiniBand vs. AM++ over MPI with a ping-pong             |    |

|     | benchmark.                                                                   | 40 |

| 3.5 | Comparison of GASNet and AM++ with a simple graph exploration benchmark.     | 42 |

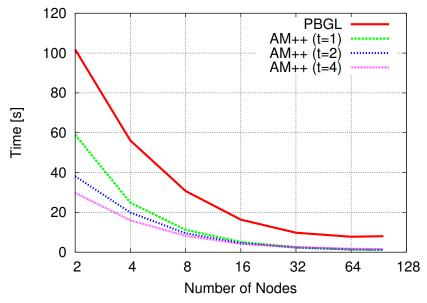

| 3.6 | Performance of the Parallel BGL (using the MPI Process Group) and AM++ with  |    |

|     | various numbers of threads performing a parallel breadth-first search.       | 45 |

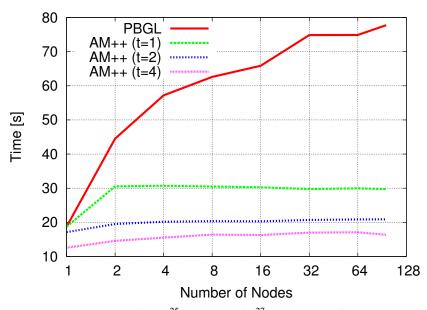

| 3.7 | Performance of the Parallel Boost Graph Library (Parallel BGL) (using the    |    |

|     | MPI Process Group) and AM++ with various numbers of threads computing        |    |

|     | single-source shortest paths in parallel using $\Delta$ -Stepping.           | 47 |

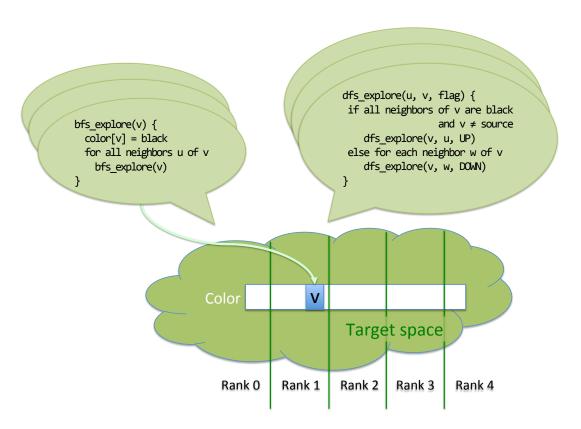

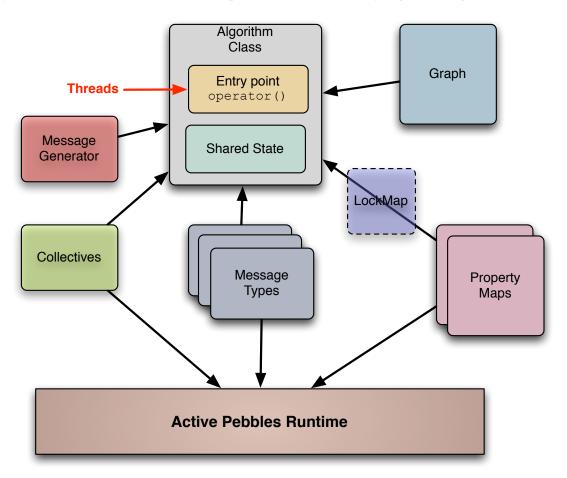

| 4.1 | Active Pebbles programming model.                                            | 55 |

| 4.2 | Active Pebbles execution model.                                              | 57 |

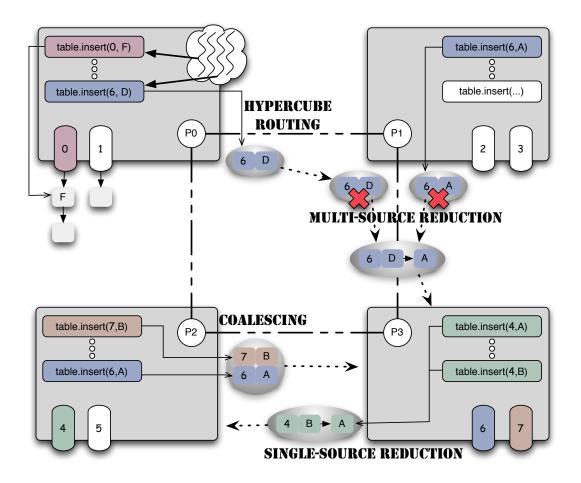

| 4.3 | Active Pebbles execution model features.                                     | 60 |

| 4.4 | Flow chart showing result of message sends to local targets.                 | 77 |

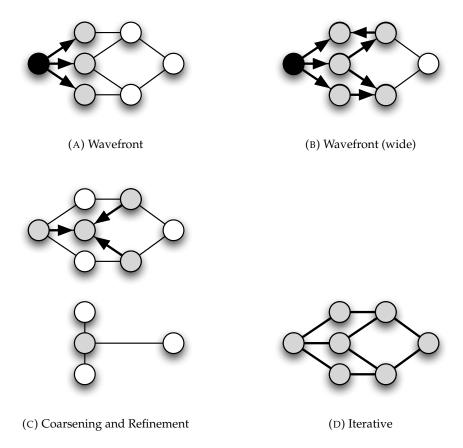

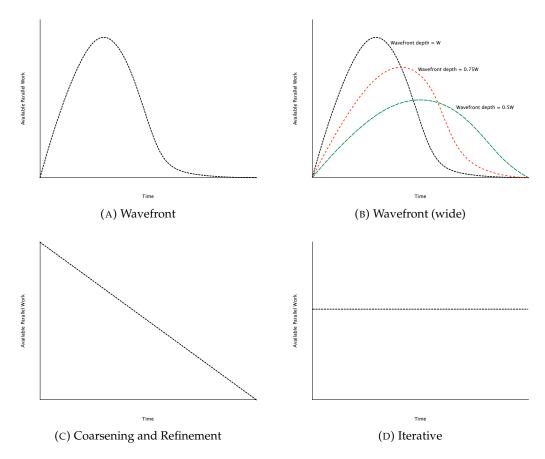

| 5.1 | Graph algorithm patterns. Grey vertices represent active vertices in the current    |     |

|-----|-------------------------------------------------------------------------------------|-----|

|     | epoch while black vertices (where present) indicate active vertices in the          |     |

|     | previous epoch.                                                                     | 81  |

| 5.2 | Illustration of how parallel work is exposed over time in each of the patterns in   |     |

|     | Figure 5.1. These charts are intended to illustrate general trends in each class of |     |

|     | algorithm and do not correspond to individual empirical data sets.                  | 82  |

| 5.3 | List of example algorithms for each of the patterns in Figure 5.1. This list is not |     |

|     | exhaustive.                                                                         | 83  |

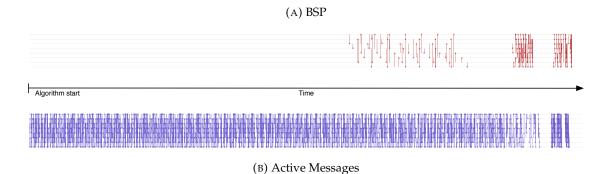

| 5.4 | Message trace of (a portion of) a breadth-first search algorithm in BSP and         |     |

|     | Active Message styles. Process ranks are represented on the Y axis. Each vertica    | Į   |

|     | arrow represents a message; arrow size is proportional to message size.             | 89  |

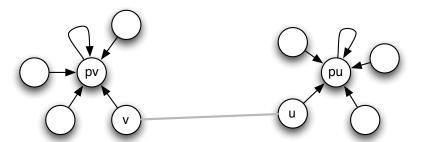

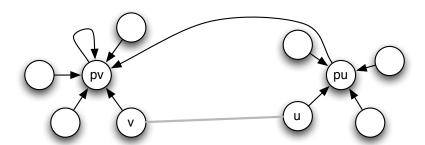

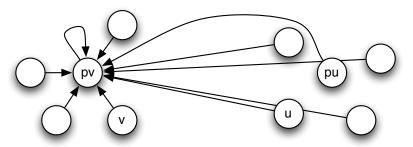

| 5.5 | Hooking and pointer doubling in Shiloach-Vishkin connected components.              |     |

|     | Black arrows indicate the parent of a vertex and the grey line represents an        |     |

|     | inter-component edge.                                                               | 93  |

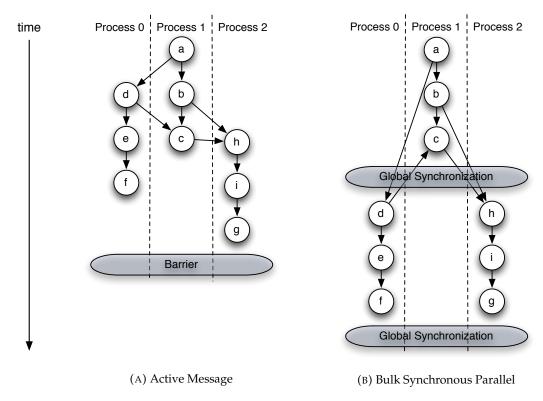

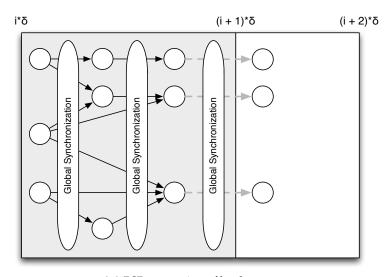

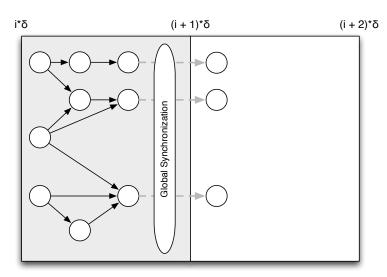

| 6.1 | Example execution of two programming models for a simple task-graph.                | 99  |

| 6.2 | Structure of Parallel BGL algorithms.                                               | 102 |

| 6.3 | Excerpt of Parallel BGL $\Delta$ -Stepping single-source shortest paths code.       | 105 |

| 6.4 | Example from Parallel BGL 2.0 connected components algorithm which                  |     |

|     | illustrates how metaprogramming is used to select between processor atomics         |     |

|     | and locking automatically.                                                          | 107 |

| 6.5 | Pseudo-PRAM version of breadth-first search.                                        | 112 |

| 6.6 | Remote-spawn version of breadth-first search.                                       | 113 |

| 6.7 | Explicit active message version of breadth-first search.                            | 114 |

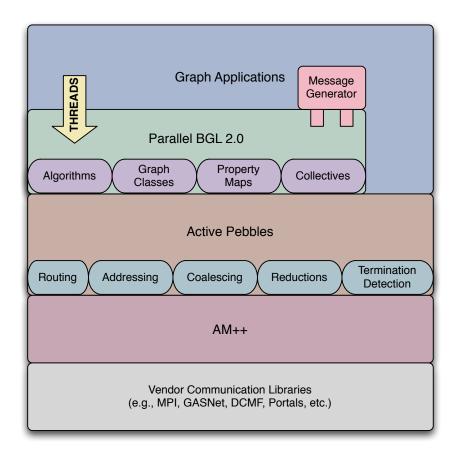

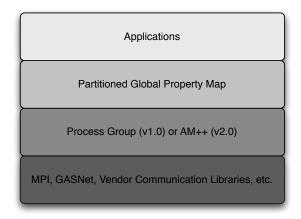

| 6.8 | Application stack using Parallel BGL 2.0, Active Pebbles, and AM++.                 | 116 |

| 6.9 | Excerpt of Parallel BGL connected components implementation.                        | 118 |

| 6.10 | Two possible instantiations of the Parallel BGL 2.0 connected component                     |     |

|------|---------------------------------------------------------------------------------------------|-----|

|      | algorithm with different messaging policies.                                                | 119 |

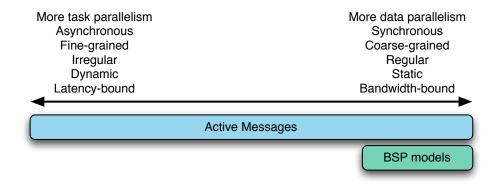

| 7.1  | Range of applications capable of being efficiently expressed by programming                 |     |

|      | models utilizing active messages or bulk synchronous parallelism exclusively.               | 122 |

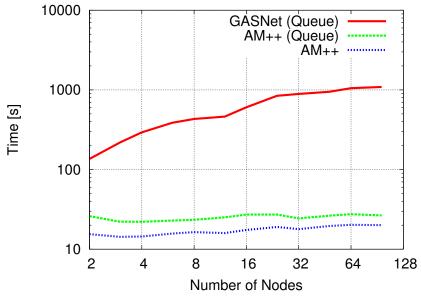

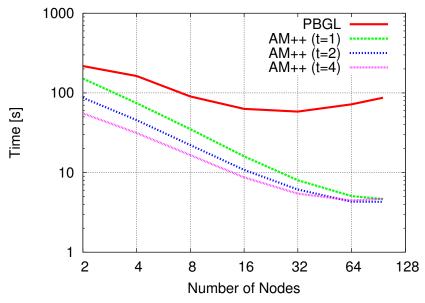

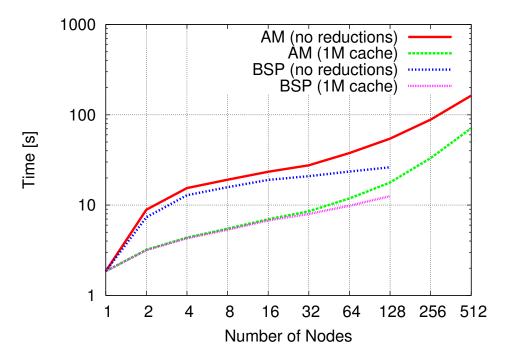

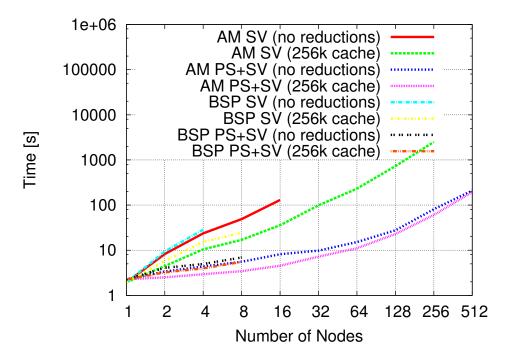

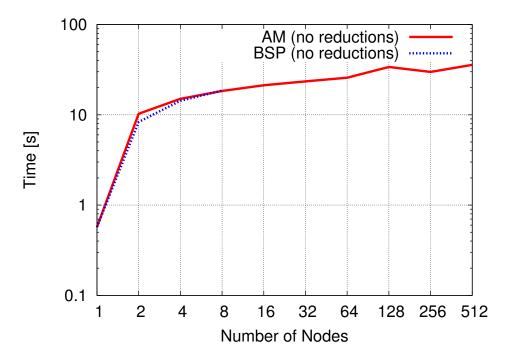

| 7.2  | Breadth-first search weak scaling (Graph 500, 2 <sup>19</sup> vertices per node, average    |     |

|      | degree of 16, 2 <sup>20</sup> -message caches, average over 16 runs which are guaranteed to |     |

|      | visit more than 100 vertices).                                                              | 131 |

| 7.3  | Communication required to process a single bucket in $\Delta$ -stepping.                    | 132 |

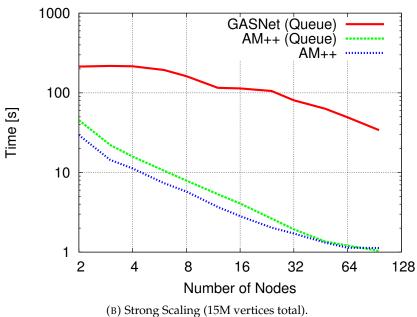

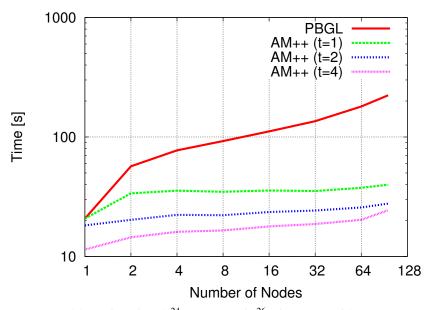

| 7.4  | $\Delta$ -stepping shortest paths weak scaling (Graph 500, $2^{16}$ vertices per node,      |     |

|      | average degree 16, 2 <sup>18</sup> -element caches).                                        | 134 |

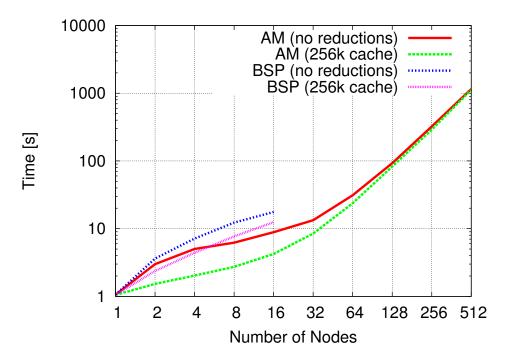

| 7.5  | Shiloach-Vishkin connected components weak scaling (Erdős-Rényi, 2 <sup>18</sup>            |     |

|      | vertices/node, avg. degree 2, 2 <sup>18</sup> -element caches). <sup>4</sup>                | 135 |

| 7.6  | PageRank weak scaling (Graph 500, 2 <sup>18</sup> vertices per node, average degree 16,     |     |

|      | average of 20 iterations).                                                                  | 136 |

| 8.1  | Distributed Property Map architecture.                                                      | 143 |

| 8.2  | Logical organization of data for a Distributed Property Map.                                | 144 |

| 8.3  | Example Distributed Property Map usage.                                                     | 148 |

| 8.4  | Example of a reducer which appends to a container.                                          | 149 |

|      |                                                                                             |     |

# List of Acronyms

| AM: Active Message                               | 22  |

|--------------------------------------------------|-----|

| <b>BFS:</b> Breadth-First Search                 | 44  |

| <b>BGL:</b> Boost Graph Library                  | 9   |

| <b>BLAS:</b> Basic Linear Algebra Subprograms    | 79  |

| <b>BSP:</b> Bulk Synchronous Parallel            | 2   |

| CORBA: Common Object Request Broker Architecture | 21  |

| CPU: Central Processing Unit                     | 7   |

| CUDA: Compute Unified Device Architecture        | 7   |

| DCMF: Deep Computing Messaging Framework         | 15  |

| <b>DSEL:</b> Domain Specific Embedded Language   | 138 |

| <b>DSM:</b> Distributed Shared Memory            | 23  |

| EC2: Amazon Elastic Compute Cloud                | 20  |

| FLOPs: FLoating-point Operations Per second      | 1   |

| FPGA: Field Programmable Gate Array              | 162 |

| GASNet: Global Address Space Networking          | 10  |

| GAS: Global Address Space                           | 60  |

|-----------------------------------------------------|-----|

| <b>GPU:</b> Graphics Processing Unit                | 162 |

| HPCC: HPC Challenge                                 | 62  |

| <b>HPC:</b> High Performance Computing              | 1   |

| KDT: Knowledge Discovery Toolkit                    | 18  |

| LAPI: Low-level Application Programming Interface   | 15  |

| MPI: Message Passing Interface                      | 3   |

| MTGL: MultiThreaded Graph Library                   | 18  |

| MX: Myrinet Express                                 | 15  |

| NIC: Network Interface Controller                   | 35  |

| <b>OFED:</b> OpenFabrics Enterprise Distribution    | 32  |

| <b>PAMI:</b> Parallel Active Messaging Interface    | 15  |

| Parallel BGL: Parallel Boost Graph Library          | 8   |

| PCIe: Peripheral Component Interconnect Express     | 7   |

| PDE: Partial Differential Equation                  | 1   |

| <b>PGAS:</b> Partitioned Global Address Space       | 13  |

| <b>PRAM:</b> Parallel Random Access Memory          | 111 |

| <b>RAII:</b> Resource Acquisition is Initialization | 38  |

| RDMA: Remote Direct Memory Access                   | 85  |

| RMA: Remote Memory Access                                  | . 138 |

|------------------------------------------------------------|-------|

| RMI: Remote Method Invocation                              | 21    |

| RPC: Remote Procedure Call                                 | 21    |

| SKR: Sinha, Kale, and Ramkumar                             | 66    |

| SMP: Symmetric Multiprocessing                             | 18    |

| SMT: Simultaneous Multithreading                           | 16    |

| <b>SNAP:</b> Small-world Network Analysis and Partitioning | 18    |

| SPMD: Single Program, Multiple Data                        | 2     |

| SSSP: Single-Source Shortest Paths                         | 46    |

| STAPL: Standard Template Adaptive Parallel Library         | 19    |

| TCP/IP: Transmission Control Protocol/Internet Protocol    | 20    |

| <b>UPC:</b> Unified Parallel C                             | 15    |

| VI SI. Very Large Scale Integration                        | 16    |

# 1

## Introduction

Coarse-grained, static, and largely data parallel applications have driven the development of the High Performance Computing (HPC) ecosystem since the inception of high performance computing. Computation and communication hardware has evolved to support these applications by focusing on floating point performance, localized communication, and highly-optimized synchronous collective operations.

The existing HPC ecosystem is effective at supporting these traditional compute intensive applications because the applications possess natural locality due to the local nature of the underlying (PDE) operators. The spatial and temporal locality in these applications provides ample opportunities for data reuse which leads to a large number of FLOPs per memory access. The spatial locality allows communication to be largely confined to a local

neighborhood, which allows effective utilization of networks with low bisection bandwidths. Finally, this natural locality allows the dependency structure of the computation to be largely determined before any portion of the computation occurs. Because locality can be determined analytically at compile-time, the granularity of the application can be coarsened through static analysis and the grouping of computations with shared data dependencies. Infrequent global synchronization can then redistribute data according to predefined patterns known to both sender and receiver between computational phases. This class of problems typically possess good separators in the dependency graph which provides balanced computation well suited to parallelization using Single Program, Multiple Data (SPMD) techniques such as the coarse-grained Bulk Synchronous Parallel (BSP) [164] "compute-communicate-synchronize" model.

A growing and increasingly diverse group of scientific disciplines including bioinformatics, social network analysis, and data mining are beginning to utilize graph analytics at HPC scales. However, graph problems have a number of inherent characteristics that distinguish them from traditional scientific applications [117]. Graph computations are often completely data-driven: they are dictated by the vertex and edge structure of the graph rather than being expressed directly in code. Execution paths and data locations are therefore highly unpredictable. Moreover, the connectivity of many graphs is not determined by physical topology (as is the case for discretized PDEs), resulting in data dependencies and computations with poor locality. Partitioning fails to provide significant benefit in such situations as no good separators may exist [63,108] and scalability can be significantly limited by the resulting unbalanced computational loads. This lack of good separators means that partitioning is unlikely to result in a sparser communication graph and provide more spatial locality than a random distribution. Finally, graph algorithms are often based on exploring the structure of a graph rather than performing large numbers of computations on the graph data, which results in fine-grained data accesses and a high ratio of data accesses to computation. Latency costs (memory accesses as well as communication) can dominate such computations.

This thesis explores a new approach to parallelizing graph applications by expressing algorithms in a fine-grained fashion and applying dynamic transformations at runtime to create efficient communication patterns. It builds on earlier collaborative work by the author and others on programming and execution models. The new work presented represents the top-most layer of a new application stack for parallel graph computation. The fundamental abstraction utilized to achieve these goals is the active message. Active messages were originally developed as part of the Split-C project [165] but are widely used today in a number of different areas. Moving control flow to data using active messages rather than using ghost cells to satisfy data dependencies allows resource utilization to be more effectively controlled. Finally, active messages provide a wealth of opportunities for parallelism at many levels provided atomic transactions on graph properties are supported to preserve the consistency of the shared data. The ability of the active message abstraction to support both coarse- (e.g., processes) and fine-grained (e.g., threads or accelerators) parallelism significantly simplifies the process of parallelizing graph applications on hardware platforms with an increasing number of levels of parallelism and diversity of hardware resources.

## 1.1. Programming Models and Graph Computation

Programming models well suited to traditional HPC applications depend heavily on the locality inherent in these applications, in particular, each node communicating with only a few local peers. Message passing is an effective programming model for these applications because it provides a clear separation of address spaces and makes all communication explicit. The Message Passing Interface (MPI) is the de facto standard for programming such systems [125]. However, graph applications need shared access to data structures which naturally cross address spaces. The access patterns induced on these data structures are both fine-grained—operating at the level of individual vertices and edges—and irregular.

A number of choices exist for how to implement fine-grained, irregular remote memory access. The key requirement with regard to graph applications is that the remote memory updates performed by one process must be atomic with regard to those performed by other processes and must support "read-modify-write" operations (e.g., compare-and-swap, fetch-and-add, etc.). More importantly, only the process performing the updates has knowledge of which regions of memory are being updated and thus the process whose memory is the target of these updates cannot perform any sequencing or arbitration of the updates. We refer to this as the "sender knowledge" case, using terminology from Holk et al. [87], as distinguished from the case where both the sender and receiver have knowledge of the destination of the updates being performed. Finally, some algorithms require concurrent, dependent updates to multiple, non-contiguous locations in memory, which provides perhaps the greatest challenge to a programming model.

The structure of graph computation is dependent on the structure of the input graph itself which is discovered dynamically at runtime. This fact makes static analysis and compile time optimization difficult and renders computational models which rely on rely on these techniques less effective. The irregular nature of graph computation and the unbalanced computational loads generated by the poor-quality partitions used to distribute them frustrate efforts at coarsening the computation at the algorithm level. Static approaches to hiding memory and communication latency are therefore ineffectual. However, techniques such as multithreading have demonstrated that asynchrony at runtime can be used effectively to hide latency. Active messages provide a mechanism to expose asynchrony both within and across address spaces. Utilizing active messages allows both memory and communication latency to be hidden effectively using a common abstraction. The active message abstraction also supports user-defined "read-modify-write" operations of arbitrarily large granularity to be expressed. In effect, active messages allow transactional memory [146] to be generalized to distributed memory.

#### 1.2. Runtime Optimization

Compile time coarsening of graph applications is unlikely to yield balanced, regular units of work which are well suited to coarse-grained parallelism due to the lack of separators required for such a decomposition [63,108]. However, fine-grained implementations are poorly suited to traditional multi-level memory hierarchies and networks. Both systems perform significantly better when moving a single large data segment vs. moving the same amount of data using multiple smaller segments. A multitude of architectural features could be discussed to support this including prefetching, caches, and network injection rate limitations to name a few. We have argued that a successful programming model for graph applications is fine grained: fundamental "graph operations" consist of individual vertex and edge accesses. Efficient implementations on modern hardware require relatively coarser-grained operations to yield maximum efficiency. This presents two implementation options:

- (1) Attempt to minimize communication overhead as much as possible and perform naïve fine-grained communication.

- (2) Attempt to apply optimizations at runtime

Given the dynamic nature of graph computations and the infeasibility of static coarsening the only choice that remains is to perform coarsening at runtime. By specifying the fine-grained structure of graph computations using active messages that operate on individual vertices and edges we preserve the full dependency structure of the computation until runtime. This allows runtime coarsening to effectively capture the critical path of the application without artificially extending it as could occur with compile time coarsening. Having the full dependency structure of the computation available allows the runtime system to make the most effective decisions possible with regard to coarsening and other potential optimizations. The drawback is that all analysis performed as a precursor to optimization contributes to the application's execution time. This thesis applies a number of optimizations to the stream of fine-grained messages generated at runtime to attempt to

recover some of the performance benefits available to other classes of applications through static analysis. These optimizations are explored in detail in Chapter 4.

Graph applications also differ markedly from more traditional HPC applications in the way in which data that is communicated is used by the application. Traditional compute-intensive applications are characterized by a high ratio of floating point operations to memory accesses. High rates of date reuse allow efficient caching of operands using traditional multi-level caches and hierarchical memory. Graph applications have much lower ratios of floating point (or integer) operations to memory operations, and thus lower rates of data reuse. Satisfying data dependencies by moving data to the site of computation is an effective strategy for traditional HPC applications because the communicated data is likely to be reused many times. In the absence of data reuse however, moving data to computation and moving computation to data may have similar communication costs.

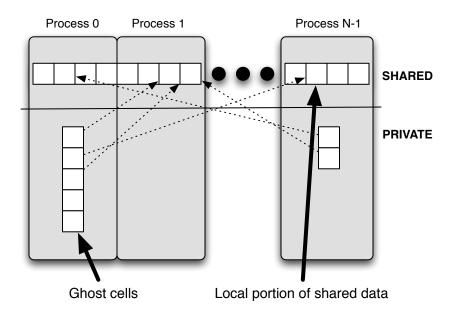

Satisfying data dependencies by moving data to the computation site has a number of drawbacks. Caching remote data using ghost cells requires additional memory and memory copy operations for the underlying storage. Maintaining the consistency of these ghost cells necessitates complicated consistency models—likely some sort of relaxed consistency to maintain efficiency—and additional communication to enforce these consistency models. Separating data flow from control flow makes reasoning about when computational dependencies have been satisfied difficult or inefficient. In traditional applications these drawbacks are balanced by high rates of data reuse and simplified communication patterns relative to unstructured graph applications.

Moving computation to data using active messages has a number of distinct advantages for graph applications. Active messages communicate control flow, possibly in combination with attached data, unifying data flow and control flow. Once a message arrives, two possible situations exist regarding its data dependencies. If all data dependencies are satisfied via a combination of local data on the receiving process and data attached to the message itself, the message can be executed and retired. If some data dependencies remain unsatisfied locally available data can be appended to the message and the message

forwarded to the owner of one of the remaining data dependencies. In this fashion messages act as closures in which the environment is updated as non-local data dependencies are satisfied. The ability to execute and retire messages during a communication epoch reduces memory utilization. This in turn allows the application as a whole to execute with less total memory, potentially allowing for more locality in the execution environment (e.g., using fewer cluster nodes or more work per node). Finally, because messages are independent and rely only on the data in the message itself and data available locally on the receiving process, greater asynchrony is available vs. programming models which rely on bulk data movement.

## 1.3. Separating Expression from Execution

The fashion in which graph algorithms are expressed need not map explicitly to the form in which they are executed. In fact, an abstract specification of an algorithm may be adapted to a variety of implementation depending on the hardware resources available. HPC is anything but immune to the many core revolution; where once clusters of workstations dominated, current machines possess an ever increasing number of levels of parallelism. To the familiar Communicating Sequential Processes model has been added multi-core parallelism within a node, hyperthreading within a core, a variety of vector units on-die, and more recently, a variety in PCIe-attached accelerators which are migrating closer to the host CPU. Abstractions that work well within a single one of these levels of parallelism have proliferated with varying degrees of success (e.g., MPI, OpenMP, CUDA, and a host of less prominent systems). Abstractions that work well across multiple levels are significantly more rare. This is evidenced by the vast preponderance of papers on combining MPI and OpenMP and exactly what number of MPI ranks vs. OpenMP threads is best suited to a particular problem.

A suitably abstract specification would be one which is capable of being mapped to all of the aforementioned hardware environments, and others that may be developed in the future, without requiring changes to the algorithm specification itself. Active messages are agnostic as to where they execute and independent of one another provided atomic access

to the data they share is ensured. This fact, in combination with their asynchronous nature, makes it straightforward to steer their execution to hardware contexts of various forms.

A naïve implementation of an active message-based algorithm may be poorly matched to a given hardware context for a variety of reasons. A single message may be too small to make efficient use of communication resources when sent alone. Handling messages individually may lead to excessive overhead or contention. Dense communication graphs between large numbers of ranks may lead to excessive communication buffer space requirements. Performance optimizations to handle these cases and many others are implemented time and again by application programmers. In traditional HPC applications these take the form of static compile-time optimizations. In the graph domain these optimizations must be deferred until runtime when the structure of the computation is discovered. Further discussion of the types of optimizations performed and their effects are discussed in Chapter 4.

These optimizations can also be separated into specification and implementation components. By having application developers specify a set of optimizations which are semantically valid for a given algorithm, users and/or the runtime can select the set of optimizations to be applied without modifying the algorithm specification. This ability to retroactively change the optimizations applied to an algorithm is the key to performance portability. Parameterizing these optimizations (e.g., on message size or routing topology) provides an additional level of control and an opportunity to auto-tune for a particular machine. Suitably generic designs allow algorithms to leverage optimizations that were unavailable when the algorithm was implemented without modification, provided the optimization is a member of a class of which the algorithm is aware. Finally, this optimization framework makes it possible for the runtime to dynamically vary optimization parameters in response to changing system characteristics.

## 1.4. Elements of an Active Message Graph Library

This thesis includes elements of three separate projects, the Parallel Boost Graph Library (Parallel BGL), AM++, and Active Pebbles. The **Parallel BGL** is a library of parallel

graph algorithms which extends the sequential Boost Graph Library (BGL) to provide distributed memory parallelism. The Parallel BGL builds on the BGL, offering similar data structures, algorithms, and syntax for distributed, parallel computation that the BGL offers for sequential programs.

The Parallel BGL was developed by lifting [77] away the implicit requirements of sequential execution and a single shared address space. The original Parallel BGL primarily utilizes a coarse-grained BSP approach communicating over MPI to parallelizing graph computation. The only available mechanism for parallelism within a shared address space is to execute additional processes. This allows algorithms to use additional cores on a single compute node, but has a number of drawbacks. First, communication between processes in the same address space is accomplished via messaging which introduces unnecessary copies compared to a straightforward ownership-transfer approach which requires only the communication of an address in the memory shared by two processes on a single node. Secondly, the Parallel BGL uses a static decomposition of the graph data consisting of a row-wise decomposition of the adjacency matrix. In the case where a single process per node exists, that process owns  $\frac{|V|}{p}$  rows of the adjacency matrix, where |V| is the number of vertices in the graph and p is the number of parallel processes. Adding k additional processes to each node to utilize additional cores results in each process owning  $\frac{|V|}{p(k+1)}$  rows of the adjacency matrix. This additional discretization of the graph data further reduces locality and exacerbates issues of computational imbalance as well as incurring additional communication overhead. These issues will be further discussed in Chapter 7.

Later in the development of the Parallel BGL, a number of extensions to improve performance and better leverage shared-memory parallelism were explored. The addition of loop-level parallelism and the incorporation of ad hoc active messages [60] to more effectively overlap communication and computation were two of the most promising extensions. The theory that re-phrasing the Parallel BGL as a purely active message based library would allow fine-grained parallelism, overlap of communication and computation, and a reduced reliance on global synchronization led to the development of **AM**++. AM++

is a generalized active message library intended for use by non-traditional HPC applications. It is targeted at a "middle ground" between low-level active message libraries such as GASNet [26] and object-based runtime systems such as Charm++ [97]. AM++ has a number of features that were important to the effort to reimplement the Parallel BGL as an active message based library:

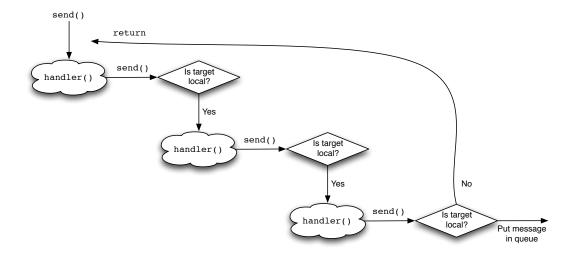

- Allowing message handlers to themselves send arbitrary messages, simplifying the expression of some applications and exposing maximum asynchrony.

- A multi-paradigm implementation, including object-oriented and generic programming, to balance runtime flexibility with high performance.

- Type-safe messages.

- A modular design enabling configurability by the user without substantial application modification.

- A design enabling compiler optimizations such as inlining and vectorization of message handler loops, and multi-threaded message handlers.

In identifying the abstractions required to design an active-message version of the Parallel BGL, two classes of abstractions were discovered. Some abstractions belonged purely to the graph domain, while others were found to be common across a broad range of data-driven applications. Of this second set, some were abstractions related to how algorithms were specified, and others were related to the efficient execution of algorithms. The abstractions common to a variety of data-driven problems were distilled into **Active Pebbles**.

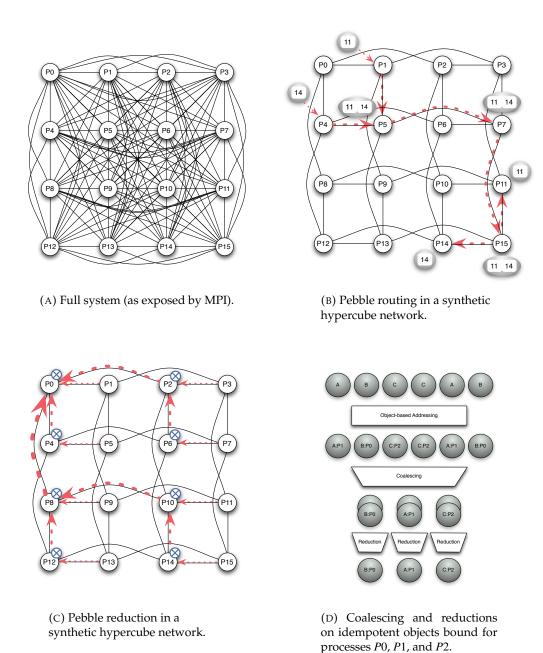

To provide the simultaneous benefits of fine-grained programmability with scalable performance, the Active Pebbles model relies on the following five integrated techniques:

- (1) **Fine-grained Addressing** light-weight global addressing to route messages to targets.

- (2) **Message Coalescing** combining messages to trade message rate for latency and bandwidth.

- (3) **Active Routing** restricting the network topology to trade message throughput for latency for large numbers of processes.

- (4) **Message Reductions** message processing at sources and intermediate routing hops (where possible).

- (5) **Termination Detection** customizable detection of system quiescence.

Messages and targets, in combination with Fine-grained Addressing (1), define an abstract programming model. The techniques in 2–5 describe an execution model which translates programs expressed using the programming model into high-performance implementations. Accordingly, techniques used in the execution model are not simply implementation details: e.g., message reductions in combination with routing cause a decrease in the asymptotic message complexity of some algorithms and are thus essential to the model.

#### 1.5. Evaluation and Contribution

This thesis demonstrates expressive and high-performance techniques for implementing parallel graph algorithms in hybrid-multicore HPC systems using active messages. By combining generic programming with active messages we have developed a conceptually simple parallel graph library (the Parallel BGL 2.0) with flexibility and adaptivity which is superior to competing solutions. By using traditional active messages with a number of novel extensions we are able to capture and utilized the fine-grained dependency structure of graph applications to out-perform coarse-grained models. Finally, the separation of expression from implementation allows a single algorithm specification to be implemented in a performance-portable fashion across a variety of hardware resources and to utilize optimizations developed independently of the algorithm itself.

- Chapter 2 introduces many of the concepts that inspired the software design proposed in this thesis.

- Chapter 3 introduces AM++ and discusses the work required to generalize active messages for use in a user-level graph library.

- Chapter 4 discusses the methods by which specification and implementation of graph algorithms are separated, using (in part) the Active Pebbles programming and execution models, in order to support retroactive optimization, auto-tuning, and dynamic runtimes.

- Chapter 5 introduces a classification of parallel graph algorithms that will be used to demonstrate the broad applicability of active messages for implementing graph algorithms.

- Chapter 6 examines, with examples, how algorithms from the literature are converted to forms suitable for expression using active messages. The methods by which possible runtime optimizations are specified are also discussed.

- Chapter 7 explores how fine-grained phrasings of graph algorithms allow greater asynchrony and parallelism than coarse-grained approaches and reduce resource utilization.

- Chapter 8 discusses the distributed property map, a pseudo-DSM layer in the original Parallel BGL which was retained to provide PGAS semantics in the active message version of the graph library.

- Chapter 9 introduces future directions for active message graph computation, including dynamic graphs and dynamic runtimes. A motivating example which demonstrates the strength of message-driven graph computation is also introduced.

- Chapter 10 summarizes the contributions of this thesis.

#### 1.6. Conclusion

The parallel programming abstractions and software design methodology presented in this thesis represent a departure from traditional HPC programming models. By removing synchronous operations and implementing algorithms in a message-driven form, we enable the critical path of fine grained applications to be accurately captured. Implementing commonly used optimizations in the runtime reduces programmer effort and allows algorithm expression to be separated from implementation.

2

# HPC Programming Models, Runtimes, and Parallel Graph Algorithm Implementations

The methodology described in this thesis represents a new approach to implementing parallel graphs algorithms that combines a communication strategy originating in dataflow programming with fine-grained shared memory parallelism and transactional updates to graph properties. This programming model is supported by a runtime system which optimizes the fine-grained message stream emitted by graph algorithms to produce efficient implementations.

In contrast to Partitioned Global Address Space (PGAS) programming models, this approach inverts the typical approach of moving data dependencies to control flow by

moving control flow to data using active messages. This technique was inspired by a number of experimental hardware platforms designed to support fine-grained shared memory programming.

The algorithm implementations discussed in this theses were influenced by a large body of parallel algorithms research as well as implementations of individual algorithms. Significant modification to algorithms was often required in order to phrase them in an active message form.

This chapter reviews many programming models targeting HPC-scale parallel applications implemented at the language, library, and runtime level. Various approaches to parallelizing graph algorithms either in the shared-memory or in the distributed-memory domain are also discussed along with their relation to the techniques in the this thesis.

## 2.1. Runtime Support for HPC Applications

A variety of relatively low-level runtime systems for supporting high-performance parallel applications have received widespread acceptance. These runtime systems can broadly be grouped into two categories: those targeted at coarse-grained distributed memory parallelism, and those targeted at fine-grained shared memory parallelism. This categories can can also be thought of in terms of data-parallelism and task parallelism respectively, with minor losses in distinction. The literature contains several architecture-focused taxonomies of parallelism which may be employed as well [57,79,140].

Pthreads (POSIX threads) is the most commonly used library on Unix-like systems for thread-based parallelism. Pthreads requires threads to be managed manually; it is designed as a low-level interface with thread creation/deletion and synchronization operations. OpenMP [46] is a set of language extensions (implemented as compiler pragmas), typically used for shared-memory computation, which simplify implementation of common threading paradigms. OpenMP is primarily designed for data decomposition. Task parallelism is an alternate method of parallelism which prioritizes work decomposition and scheduling over data decomposition. Task parallelism is often implemented in an ad hoc fashion, but robust runtime systems such as Intel's Threading Building Blocks [89],

Microsoft's Task Parallel Library [112], and PFunc [99] are gaining increased support. Cilk and Cilk++ [24] are language extensions to C/C++ which both provide support for task parallelism as well as incorporating runtime scheduling and load balancing.

Messaging-based approaches are commonly utilized when a global shared address space is not available or is impossible to implement efficiently. MPI [56, 123] is the de facto standard library for message passing in parallel computing. It assumes a distributed-memory model, with communication and synchronization explicit and implicit for both the sender and receiver of data. Later versions of MPI are less restrictive; they allow one-sided remote memory operations that only require explicit action by the sender. Classical MPI-1 [123] programs are epoch-based and frequently use a strict BSP [164] programming model. MPI-2 [125] extensions provide extended collectives, one-sided communication, and dynamic process management. Non-blocking collectives from libraries such as libNBC [85] further extend the flexibility of MPI and have been included in MPI-3 [126], along with more powerful one-sided communication operations. Algorithms for dynamic sparse data exchange such as [86] have the potential to improve the performance of graph algorithms implemented using message passing and collective communication.

Alternatives to MPI include a variety of active message libraries which allow user-defined code to be invoked asynchronously on a remote process. Examples of these libraries include IBM's Deep Computing Messaging Framework (DCMF) [106], Low-level Application Programming Interface (LAPI) [143], and Parallel Active Messaging Interface (PAMI) [105]; Myrinet Express (MX) [74]; and GASNet [26]. Systems such as Unified Parallel C (UPC) [163], Co-Array Fortran [128], a number of MPI implementations, and object-based programming systems all rely on active messaging for their low-level transport. Using active messages directly in an application is frequently difficult because the interfaces to existing active message systems are very low-level.

### 2.2. Architectures, Languages, and Programming Models

Research into next-generation parallel computing platforms, languages, and programming models has been focused on two broadly-defined areas. First, a variety of hardware

approaches have sought to provide high levels of on-chip parallelism to both increase instruction throughput and reduce or hide memory and network latency. Second, languages and libraries have been developed to reduce the conceptual burden of programming distributed and heterogeneous systems.

Early research into on-chip parallelism led to fine or interleaved [109] multithreading approaches with extremely cheap switching between hardware thread contexts [151]. Fine-grained multithreading is effective at hiding memory latency, but suffers when there is inadequate parallelism available to utilize all the available parallel contexts. Simultaneous Multithreading (SMT) is a more recent evolution of this approach to hiding latency. Niagara [103] is a processor architecture from Sun (now Oracle) that relies heavily on inprocessor SMT. The Cray XMT [64] (based on the Tera MTA [10] series) is a more extreme version of an SMT approach, designed for programs with thousands of threads. In that system, threading is used to hide memory latency; sophisticated hardware-supported lightweight synchronization operations are provided to communicate between the threads. The IBM Cyclops64 [9] is another highly multi-threaded architecture distinguished by the fact that rather than providing inexpensive thread context switching, each thread context has its own execution hardware. Other approaches to addressing memory latency include approaches such as the J-Machine [47] which utilize VLSI techniques to embed lightweight processors in memory systems. Later microprocessor designs, such as Sparcle [5], combine latency tolerant architectures, optimized fine-grained synchronization, and fast message handling to allow them to be combined into large-scale multiprocessors [4].

The PGAS model, as exemplified by Titanium [174], UPC [163], and Co-array Fortran [128], is an approach that mixes shared- and distributed-memory semantics. The use of remote data is explicit in computations, yet global pointers can be used to access remote objects. X10 [39] and Chapel [32] are PGAS languages which provide support for programming models beyond simple data parallelism. These languages combine PGAS-style support for data parallelism with support for task parallelism via asynchronous spawning primitives, nested parallelism, and fine-grained concurrency. PGAS frameworks have

identified and are addressing limitations in their handling of graph algorithms. For example, Jose et al. introduced UPC Queues, a mechanism for faster producer-consumer communication in the context of Unified Parallel C [94]. The goal of this work is to improve UPC's performance on the Graph 500 benchmark [127] (breadth-first search).

The Chapel [32] language provides direct support for asynchronous active messages using the *on ... do begin* idiom [50], as well as native atomic blocks. This model inspired one of the intermediate languages described in Chapter 6 § 6.2, and (if combined with an appropriate execution model) would be a suitable abstraction for expressing graph algorithms using the approach described in this paper. The X10 language [39] has similar constructs using *async* and *at* keywords for sending active messages. That language has been used to create the ScaleGraph [48] graph library; however their implementation techniques are not described. The default execution models for these languages do not provide efficient support for messages at the fine granularities we use for graph algorithms, however.

Message-driven and dataflow models are similar to the PGAS languages in that they are data-parallel, but emphasize the connections between computations rather than the computations themselves. The Actors [6] model uses messages rather than sequential processes to convey both control and data. Dataflow languages similarly treat data as the primary concept behind any program and use data inputs to define control flow. Coordination languages such as Linda [73] treat process coordination as a separate activity from computation.

### 2.3. Parallel Graph Algorithm Implementations

A number of libraries targeted at parallel graph computation exist which utilize a variety of abstractions. The original version of the Parallel BGL [77] utilized a coarse-grained Bulk Synchronous Parallel [164] programming model and targeted only distributed memory parallelism. Later extensions added some ad hoc forms of active messaging, though the performance of these approaches is limited by the underlying communication layer. By abstracting these features into a separate layer in the application stack we have gained

generalization, flexibility, and through careful design, performance. This separate, thread-safe active message layer also made incorporating fine-grained parallelism (via threading) straightforward. We refer to the new active message-based version of the Parallel BGL as Parallel BGL 2.0.

The Graph Algorithm and Pattern Discovery Toolbox [76], later renamed the Knowledge Discovery Toolkit (KDT), provides both combinatorial and numerical tools to manipulate large graphs interactively. KDT runs in parallel over Star-P [144] and targets distributed memory parallelism. KDT focuses on algorithms though the underlying sparse matrix kernels are also exposed. Later versions of KDT use the Combinatorial BLAS [31] as the computational back-end. The Combinatorial BLAS uses linear algebraic primitives to perform graph computation and incorporates two-dimensional data decompositions. Whether viewing the underlying data structure as a graph or a sparse matrix is more appropriate depends on the operations required by a given algorithm. In some cases, both types of solutions are equally effective, while in others, either a graph or sparse-matrix representation may be preferable. We view sparse-matrix libraries as providing complementary functionality to parallel graph libraries and have previously demonstrated the ability to enable the Parallel BGL to interoperate with other generic libraries such as the Iterative Eigensolver Template Library [28,160]. Similar techniques may enable the graph library presented here and other libraries, such as the Combinatorial BLAS, to interoperate, thus enabling algorithm implementations which employ primitives from both libraries on the same underlying data. Because both the Parallel BGL 2.0 and the Combinatorial BLAS are generic libraries it should be straightforward to allow the libraries to operate on each other's underlying data representations, providing users a choice of abstractions and allowing them to select the one best suited to their problems, or mix and match the two.

The MultiThreaded Graph Library (MTGL) [23] and Small-world Network Analysis and Partitioning (SNAP) [15] are shared-memory libraries for manipulating graphs and are thus limited to the resources available on a single symmetric multiprocessor. The MTGL uses loop-level parallelism and complicated dependency analysis to generate efficient code for the Cray XMT and, via virtualization, commodity SMPs [170]. MTGL is not as generic

as the Parallel BGL is in terms of supported graph types and algorithms. STINGER [58] extends shared-memory parallel graph processing to streaming, dynamic networks. Experimental results indicate that out-of-core approaches are incapable of matching the performance of distributed-memory implementations [7] meaning that implementations capable of leveraging both shared and distributed memory parallelism are essential for graph computation at large scale.

Several distributed-memory parallel libraries provide graph algorithms and data structures. The ParGraph library [84], also built on top of the sequential BGL, provides generic max-flow and breadth-first search implementations, although it opts for a more explicit representation of communication that does not permit reuse of, e.g., breadth-first search in the parallel context. The CGMgraph library [34,35] is an object-oriented library for distributed graph computation. The Standard Template Adaptive Parallel Library (STAPL) [11] is a generic, parallel library modeled after the Standard Template Library and providing distributed data structures and parallel algorithms, including a graph data type. Where the Parallel BGL has opted to encode distribution and parallel communication information within the data types and selects efficient algorithms at compile time, STAPL delays such decisions until run-time to adapt to the current execution environment. STAPL is built upon the ARMI active-message runtime system [158]. ARMI supports automatic message coalescing to coarsen message granularity for performance, but does not provide routing or message reductions natively. STAPL's parallel graph class pGraph is based on the sequential Boost Graph Library, and some of its algorithms use nested active messages to create distributed-memory parallelism, but details are not provided [157].

The popularity of high-level, data-parallel frameworks such as MapReduce [49] and Dryad [91] and the widespread availability of cloud-computing resources have driven a number of efforts to adapt these resources to application domains with complex dependency structures such as graph processing. Extensions such as Spark [176] extend these frameworks to iterative computation. Pegasus [100] is a collection of graph algorithms for mining large graphs using Hadoop [171]. The vast majority of libraries and tools suitable for parallel graph computation such as Pregel [120], Giraph [3], and Piccolo [135] are based

on the BSP model. Chapter 7 examines in detail why this model is suboptimal for parallel graph computation. GraphLab [116] is a framework for machine learning and data mining in the cloud. It attempts to provide additional asynchrony compared to other coarse grained cloud-based graph algorithm implementations. GraphLab relies on the availability of good partitions in the graph being mined or, in the absence of trivial colorings, distributed locking. GraphLab uses a similar combination of ghost cells and pulling data dependencies to computation as the original Parallel BGL. Performance results indicate that GraphLab is unable to outperform even highly-synchronous MPI codes when the ratio of communication to computation is small or the input graph does not provide for good partitions with small edge cuts. The MPI codes compared against were running over TCP/IP in Amazon Elastic Compute Cloud (EC2) [2], which means that their performance was likely to be significantly worse than what would be expected on a dedicated cluster with a highspeed, low-latency interconnect and collectives optimized for the interconnect's topology. Cloud-based solutions fill an important gap for users without access to dedicated HPC resources but are unlikely to provide competitive performance on latency-bound computations due to the limitations of the IP networks utilized. Data-mining applications are more loosely coupled and suffer less from these high latency networks. Thus, cloud-based solutions are largely focused on these types of applications as opposed to traversal-based algorithms.

A variety of individual implementations of graph algorithms that leverage shared-memory parallelism on both commodity and highly multi-threaded architectures exist, such as those by David Bader and Kamesh Madduri [16, 18, 119]. Examining a variety of concrete implementations is the first step in the lifting process through which effective abstractions are identified and generic libraries are developed. These existing shared memory implementations can be used to improve algorithm implementations presented here. Individual examples of distributed memory graph algorithms do exist [175] as well, and provide useful insight for mapping graph algorithms to distributed memory HPC platforms.

Exposing simplified interfaces through higher-level languages or new abstractions is an excellent way to extend the impact of library implementations to a broader range of application developers and scientists. Various efforts exist to express a high-level interface to unstructured problems [75,104,144]. Effective abstractions are seldom developed in a top-down fashion however. High-level interfaces often benefit from very efficient lower-level library implementations as well. The graph library presented here is beneficial to these types of efforts both in that it provides a flexible, efficient, robust framework for high-level interfaces to target, and because through its development we discover new programming abstractions in a bottom up manner.

## 2.4. Active Messages

Previous libraries supporting active message or Remote Procedure Call (RPC) semantics can be broadly grouped into two categories: low-level and high-level. Low-level systems are meant for other libraries and run-time systems to build upon, or to be used as a target for compilers; performance is the most important goal, with flexibility less important. These libraries do not provide type safety for messages and often have arbitrary, frequently system-specific, limits on the number and types of parameters to an active message, actions that can be performed in active message handlers, etc. As these libraries assume a sophisticated user, features such as message coalescing are not always provided. Libraries such as IBM's DCMF [106], LAPI [143], and PAMI [105]; MX [74]; and GASNet [26] are typical examples. GASNet's manual states that it is not intended for direct use by applications [26, §1.2], while DCMF, LAPI, and PAMI are intended for such use.

On the other hand, libraries in the RPC tradition are designed for usability, often at the expense of performance. These libraries tend to be more flexible, and more likely to support heterogeneous systems, interface discovery (including sophisticated interface definition languages), and security; run-time dispatch is used heavily, but type checking is usually provided. Some RPC systems expose individual functions for remote access, while others expose objects and their methods. Examples of traditional RPC systems include Java RMI [166], CORBA [129], and ONC RPC [159].

Some authors have implemented systems based on RPC principles that are intended for high-performance computing applications. These systems trade off some of the flexibility of fully general RPC in exchange for higher performance. They also include techniques such as message coalescing to reduce message counts, and rely on asynchronous method calls to hide latency. These systems include Charm++ [97,148] and ARMI [158]. The ParalleX system is also based on active message/RPC principles, with sophisticated methods for locating possibly-migrated remote objects and non-message-based synchronization methods [96].

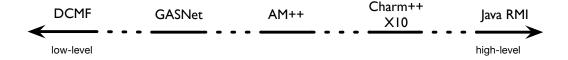

Our work differs from these systems in that it does not use objects as the target of remote accesses; we instead use functions registered as handlers. Our messages target nodes, not single objects. Because we allow C++ function objects, methods could be used as AM++ handlers as well by adding an explicit parameter representing the object being addressed, but that is not the intended use case. We provide the flexibility of arbitrary actions (including active message sends) in message handlers like in RPC systems, but use a fully asynchronous model: a message is not guaranteed to be sent until an explicit synchronization operation. We additionally avoid run-time dispatch for our higher-level interfaces using the techniques of generic and generative programming; the compiler is able to resolve that an entire buffer of coalesced messages is all intended for the same handler, and optimize accordingly. We therefore are in the middle, between the low-level Active Message (AM) implementations with their focus on performance and the higher-level systems with their focus on ease of use (Figure 2.1); our goal is a mix of both.

FIGURE 2.1. Comparison of AM++ vs. other active message implementations

The MPI standard defines *one-sided* operations [125, §11] which are in some sense similar to active messages with predefined handlers. Those operations allow users to access remote memory (put and get) and perform calculations on remote memory (accumulate).

The latter is probably closest to the concept of active messages; however, MPI specifies a fixed set of possible operations and does not currently support user-defined accumulations. Additions to one-sided operations in MPI-3 [126, ch. 11] such as MPI\_Fetch\_and\_op() and MPI\_Compare\_and\_swap() may also rectify some of the shortcomings of the MPI one-sided communication model, though high performance implementations were unavailable when this work was conducted. MPI-3 does not allow user-defined functions to be used with these additional one-sided operations which prevents their utilization as a basis for generalized active messages.

PGAS languages such as UPC [163] and Co-Array Fortran [128], are comparable to AM++ in that they are both trying to provide user-level interfaces to AM and one-sided messaging. The Berkeley UPC compiler's runtime system uses GASNet for communication [41]. However, these languages primarily use active messages and one-sided operations for data movement, not for the implementation of user algorithms. AM++ exposes the ability to use active messages for algorithm implementation.

### 2.5. Distributed Shared Memory and Transactional Memory

Distributed Shared Memory (DSM) [136] allows applications written for shared-memory models to execute on distributed memory systems by emulating a single shared address space. Many DSM systems treat the disjoint physical address spaces as an additional level in the memory hierarchy and use page-based approaches similar to those utilized by virtual memory systems to move data in the logically shared address space to individual physical address spaces where it can be operated on. While page-based approaches make addressing objects in the shared address space straightforward, they also increase the likelihood of false sharing relative to more fine-grained approaches. This concern is magnified by the fact that many DSM systems use some form of release consistency. DSM models that use weak consistency models suffer from the issues in the original Parallel BGL design where excessive memory barriers group accesses in a fashion that makes exploiting fine-grained dependency structure difficult.

Object-based DSM systems also exist to address the granularity issues some applications experience when using page-based DSM systems. Adsmith [115] is an object-based DSM system with an addressing scheme similar to distributed property maps in the original Parallel BGL. However, Adsmith uses release consistency and only implements loadstore semantics whereas distributed property maps implement richer semantics for manipulating shared objects and enforces consistency without explicitly acquiring and releasing objects. Object-based DSM extensions to Aleph [81] also exist [95]. The global associative tuplespace in Linda [73] is another example of an object-based DSM. Object-based DSM systems which use weak consistency models can be used to implement graph algorithms, as shown in the original Parallel BGL design, and are similar to distributed property maps. One of the claims of this thesis is that moving data to computation is sub-optimal in unstructured computations and that models which move computation to data have higher performance.

In some sense active messages which can perform arbitrary operations as in AM++ extend memory transactions to distributed memory, provided transactions are supported within address spaces. Memory transactions are, in the simplest case, simply a group of memory operations which are guaranteed to be observed atomically. Memory transactions can be implemented with locks or critical sections, however lock-free and wait-free approaches provide better performance [82]. Transactional memories provide support for this behavior directly in the system architecture [83]. A variety of methods for emulating transactional memory in software have been explored [146]. The programming model and algorithm implementations in this thesis would benefit greatly from hardware support for transactional memory and extending the work to leverage them would be straightforward.

### 2.6. Conclusion

The work presented in this thesis is based on two primary observations about parallel graph algorithms. First, graph algorithms lack a fixed computation or communication structure that can be analyzed and statically optimized at compile time. The structure of the application is defined by the input graph which is discovered at runtime. Second,

these algorithms have a low ratio of computation to communication making them highly sensitive to memory and network latency. Furthermore, they have little spatial or temporal locality rendering traditional hierarchical caches ineffective.

Coarse-grained, bulk-synchronous parallel implementations of graph algorithms exist in a number of forms. A variety of programming abstractions exist to support this method of parallelism including the MapReduce pattern and PGAS languages<sup>1</sup>. These coarse-grained approaches create artificial dependencies as a result of their static work decompositions and fail to capture the fine-grained critical path of graph applications. Efficient graph algorithm implementations are distinguished by their ability to generate maximal parallelism while minimizing latency due to memory access or contention, including access to remote data in the case of distributed-memory. Inspired by a number of hardware techniques for leveraging asynchrony to tolerate latency we have elected to pursue an approach that combines fine-grained expression with runtime optimization to generate efficient implementations for hybrid environments containing distributed-memory machines with a variety of shared-memory, parallel resources.

Virtual memory [22] is an excellent example of how a single abstraction (the virtual address space) can allow users to efficiently manipulate extraordinarily complex, multi-level systems (the physical memory hierarchy). Rather than a two-level approach to parallelism (e.g., MPI + OpenMP) we have been able to extend an existing parallel programming abstraction, active messages, to provide for efficient parallel performance at multiple levels. This reduces the cognitive burden on the user and allows for a broader variety of possible implementation contexts and optimization opportunities.

In order to allow active messages to directly express algorithms without requiring external sequencing and arbitration, a number of extensions were required. These extensions are discussed in Chapter 3. Additionally, in order to optimize communication performance